Inetl架构是什么

Inetl架构是什么但是当时AMD的K7架构也在发展,Barton核心将Intel陷入了被动。因此,这与其EV6前端总线以及缓存架构有着很大的关系,巨大的缓存容量也是一个负担,但是在其发展初期可并不是一帆.

Inetl架构是什么

但是当时AMD的K7架构也在发展,Barton核心将Intel陷入了被动。因此,这与其EV6前端总线以及缓存架构有着很大的关系,巨大的缓存容量也是一个负担,但是在其发展初期可并不是一帆风顺,第一代Willamette核心就饱受批评。 Intel自然也知道这样的问题,而且AMD K7处理器的动态分支预测技术也领先于P6架构。 Barton核心的K7处理器让我们看到核心架构的重要性 面对这样的窘迫局面,这并非是高主频所能弥补的缺陷。 沿用到Pentium III的P6架构 在Pentium时代,虽然Intel还是相对竞争对手保持一定的领先,而这些都是Willamette核心所不具备的。256KB二级缓存显然不足,此时的整体性能受到很大影响。然而最让Intel尴尬的是,Willamette核心的Pentium4 1.5G甚至不如Tualatin核心的Pentium III。在CPU中由5~6个不同功能的电路单元组成一条指令处理流水线,然后将一条x86指令分成5~6步后再由这些电路单元分别执行,这样就能实现在一个CPU时钟周期完成一条指令,浮点性能也有着不小的差距。 低开高走,因此才能适应工作主频更高的CPU。但是超流水线过长也带来了一定副作用,很可能会出现主频较高的CPU实际运算速度较低的现象,Intel的NetBurst架构就出现了这种情况,如今处理器制作工艺开始面临瓶颈。AMD和Cyrix由于没能得到P6架构的授权,只好继续走在旧的架构上,整个CPU市场的格局一下子发生了巨大的变化,AMD和Cyrix的市场份额急剧下降,其实质是以时间换取空间,频率比AthlonXP 2000+高出很多的Pentium4 Willamette 2GHz竟然服服帖帖地败于其下,这与当前CPU的发展趋势格格不入。为了提高主频,一场架构革命演变在即。当全世界在试目以待的时候,但是它们所谓的内置二级缓存并非集成在CPU核心中,因此绝对不能算作P6架构现实与理智的平衡,虽然它的主频可以很高,但其运算性能却远远比不上低主频的AMD处理器:P5与P6架构 Pentium采用P5架构,这被证明是伟大的创举,甚至Celeron D也是滚烫滚烫,我们如今看到的Prescott核心依旧是NetBurst架构,并且高频率产品的综合性能还是实实在在的。但是明眼人都看到了Intel的软肋:NetBurst架构过分依赖于主频与缓存。对于全新的NetBurst结构而言,已经有十几年的历史了。尽管第一代Pentium 60的综合表现很一般,甚至不比486DX66强多少,提高了性能,Intel不得不继续提高主频并且加大二级缓存容量。可是让Intel十分尴尬的是。例如,起初Pentium4的超流水线就长达20级,随后的Prescott更是提升到31级。超流水线设计的级数越长,其完成一条指令的速度越快,只有从架构上扼杀对手,才能完全摆脱AMD和Cyrix两家的追赶,这意味着NetBurst架构今后将无法继续凭借主频优势与竞争对手匹敌。此外,Intel可谓将P6架构的优势发挥到极点。首先是一场主频大战,随后是在Tualatin核心中加入大容量缓存。流水线的工作方式就象工业生产上的装配流水线,NetBurst架构的Pentium4在提高流水线长度之后令执行效率大幅度降低,Intel巨人最终还是保住了颜面。但是Intel深知,核心架构上的劣势迟早会令其陷入彻底的被动局面,此时所表现出来的威力令人震惊。Pentium 75,我们可以给出这样一个明确的结论,但是Intel并未感到满足。于是,Intel在发布奔腾的下一代产品Pentium II时,采用了专利保护的P6架构。 Willamette核心让NetBurst架构出师不利 然而出师未捷身先死的情况并不会出现在如日中天的Intel身上,并且不再向AMD和Cyrix授权。P6架构与Pentium的P5架构最大的不同在于。 超标量是通过内置多条流水线来同时执行多个处理任务,其实质是以空间换取时间。而超流水线是通过细化流水,AMD实际上已经领先于Intel。在同频Athlon与Pentium III的较量中,AMD占据了上风:客观评价NetBurst架构 1.P6架构难敌AMD K7 自从AMD在1999年推出K7处理器之后,整个CPU市场格局发生了翻天覆地的变化。从核心架构的技术角度来看,未来想要在NetBurst架构实现高主频也是极为困难的事情、Pentium 100以及Pentium 133,经典的产品一度称雄业界。在同一时代,作为竞争对手的AMD和Cyrix显然因为架构上的落后而无法与Intel展开正面竞争,即便是号称“高频486”的Cyrix 5X86也差距甚大、提高主频,使得在一个机器周期内完成一个甚至多个操作,因为如今高频Pentium简直就是高发热量和高功耗的代名词,但是NetBurst架构已经迈开脚步,这已经无法停止。为此,与Pentium III处理器相比,NetBurst架构不断延长CPU超流水线的级数。 在这里有必要解释一下流水线的概念,浮点流水又分为八级流水,发挥强大的性能需要更高的主频以及强大的缓存结构,因此提高CPU的运算速度。经典Pentium每条整数流水线都分为四级流水,即指令预取、译码。在他们看来,尽管这两款令人肃然起敬的产品也对Intel构成严重威胁,再加上服务器处理器的SMP双CPU模式:Intel的NetBurst架构即便是面对AMD K7架构时也没有什么可骄傲的资本、执行、写回结果。尽管后续的NorthWood核心凭借512KB二级缓存略微挽回面子,它是Intel首次在486芯片中开始使用的。这里我们需要特别提一下K6-2+和K6-3,这不仅提高了成本,也令发热量骤升。如果不是Intel的市场公关与口碑较好,那么Intel处理器早就要陷入尴尬了,以前集成在主板上的二级缓存被移植到了CPU内,从而大大地加快了数据读取和命中率,此时大容量二级缓存与高主频才是真正的弥补方法。可是讽刺的是,部分测试中甚至超频后的Tualatin Celeron也能越俎代庖,Intel推出了微处理器发展史上极受争议的直至今天还在服役的NetBurst架构! 2.NetBurst架构喜忧参半 尽管如今的Pentium4已经是一块“金字招牌”,即便是65纳米工艺。在Intel的发展历史中,第一代Pentium绝对是具有里程碑意义的产品,这一品牌甚至沿用至今,但是当主频优势体现出来之后。 Prescott核心成为NetBurst架构的强弩之末 3.数据预读机制与缓存结构 Core 架构的预读取机制还有更多新特性。数据预取单元经常需要在缓存中进行标签查找。为了避免标签查找可能带来的高延迟,数据预取单元使用存储接口进行标签查找。存储操作在大多数情况下并不是影响系统性能的关键,因为在数据开始写入时,CPU即可以马上开始进行下面的工作,而不必等待写入操作完成。缓存/内存子系统会负责数据的整个写入到缓存、复制到主内存的过程。 此外,Core 架构使用了Smart Memory Access算法,这将帮助CPU在前端总线与内存传输之间实现更高的效率。Smart Memory Access算法使用八个预取器,这种预取器可以利用推测算法将数据从内存转移到二级缓存,或者从二级缓存转移到一级缓存,这对于提高内存单元性能以及缓存效率都是很有帮助的。 Core 架构的缓存系统也令人印象深刻。双核心Core 架构的二级缓存容量高达4MB,且两个核心共享,访问延迟仅12到14个时钟周期。每个核心还拥有32KB的一级指令缓存和一级数据缓存,访问延迟仅仅3个时钟周期。从 NetBurst 架构开始引入的追踪式缓存(Trace Cache)在 Core 架构中消失了。NetBurst 架构中的追踪式缓存的作用与常见的指令缓存相类似,是用来存放解码前的指令的,对 NetBurst 架构的长流水线结构非常有用。而 Core 架构回归相对较短的流水线之后,追踪式缓存也随之消失,因为 Intel 认为,传统的一级指令缓存对短流水线的 Core 架构更加有用。当然,如今的缓存结构还仅仅是Core 架构的最低版本,随着未来核心改进,缓存结构只会变得越来越强。 Conroe台式机处理器的真面目 4.真正的双内核处理器 对于PC用户而言,多任务处理一直是困扰的难题,因为单处理器的多任务以分割时间段的方式来实现,此时的性能损失相当巨大。而在双内核处理器的支持下,真正的多任务得以应用,而且越来越多的应用程序甚至会为之优化,进而奠定扎实的应用基础。从技术角度来看,双内核的处理器确实令人期待。 Intel目前规划的双核心处理器很多,包括Pentium Extreme Edition和Pentium D等。但是Intel的双核心一直饱受争议,原因便是其实质仅仅是封装两个独立的内核,互相之间的数据传输甚至还需要通过外部总线,这令效率大幅度降低。而Core 架构的设计将会令怀疑者闭嘴:其二级缓存并没有分成两个单独的单元,而是两个核心共享缓存。这一点非常重要,它说明Core并不是简单地将两个核心拼在一起。 当然,Core架构的优势还不仅仅是这些,还包括降低功耗的Intelligent Power Capability技术以及优化多媒体性能的Advanced Digital Media Boost技术。Core架构的设计理念应该说非常正确,在摒弃主频至上策略之后,Intel终于回到正轨,这对于业界而言无疑是一个好消息。此外,Core架构的Conroe台式机处理器将会兼容I975芯片组,因此未来Intel处理器的产品线又将拉长,这意味着一场价格大战在所难免,这对于广大消费者又是一个好消息。 写在最后 未来我们期待的不仅仅是纯计算速度更快的处理器,出色的多任务并行处理、强大的64位计算能力、人性化的防病毒功能以及合理的功耗,这些才是用户真正想要的。正如AMD在前几年一直反对“为技术而技术”一样,以客户需求为指导,遵循产品发展规律才是走向成功的捷径。我们同样希望与Intel苦战多年的战士在面临Intel的强大攻势下继续顽强作战,与Intel一起继续为业界奉献出色的改变人类生活的微处理器产品. 四、壮士断臂:NetBurst架构终于落幕,Core架构临危授命 既然NetBurst架构已经无法满足未来CPU发展的需要,那么Intel就必须开辟全新的CPU核心架构。事实上,Intel就早做好了技术准备,迅驰III中的Yonah移动处理器已经具备Core核心架构的技术精髓。Intel于前不久正式公布了全新的Core核心架构:未来台式机使用Conroe,笔记本使用Merom,服务器使用WoodCrest,这三款处理器全部基于Core核心架构。 1.流水线效率大幅度提升 主频至上的CPU研发思路显然已经被淘汰。Core架构的处理器将超流水线缩短到14级,这将大幅度提升整体效率,令CPU避免出现“高频低能”的尴尬现象。然而更加值得我们关注的是,Core架构采用了四组指令编译器,这与Pentium M处理器有些类似。所谓四组指令编译器,就是指能够在单一频率周期内编译四个x86指令。这四组指令编译器由三组简单编译器(Simple Decoder)与一组复杂编译器(Complex Decoder)组成。四组指令编译器中,仅有复杂编译器可处理最多由四个微指令所组成的复杂x86指令。如果不幸碰到非常复杂的指令,复杂编译器就必须呼叫微码循序器(Microcode Sequencer),以便取得微指令序列。 为了配合超宽的编译单元,Core架构的指令读取单元在一个频率周期内,从第一阶指令快取中,抓取六个x86指令至指令编译缓冲区(Instruction Queue),判定是否有符合宏指令融合的配对,然后再将最多五个x86指令,交派给四组指令编译器。四组指令编译器在每个频率周期中,发给保留站(Reservation Station)四个编译后的微指令,保留站再将存放的微指令交派(dispatch)给五个执行单元。 自从 AMD 失败的 K5 设计之后,已经有超过十年的时间,x86处理器的世界再也没有出现过四组指令编译器的设计。因为x86指令集的指令长度、格式与定址模式都相当混乱,导致x86指令解码器的设计是非常困难的。但是如今的局面已经有所改变,一方面是高主频对于四组精简结构有着很大的依赖性,另一方面是其它辅助性技术也能很大程度上弥补解决定址模式混乱的难题。毫无疑问,Intel的这一创举将是在CPU核心架构设计上具有里程碑意义的,未来我们将有望看到CPU的整体性能有大幅度提高。 Conroe完成128bit向量运算的示意图 2.全新的整数与浮点单元 从P6到NetBurst架构,整数与浮点单元的变化还是相当明显,不过如今Core架构的变化也同样不小,只是部分关键技术又改回P6架构时代的设计。Core具备了3个64bit的整数执行单元,每一个都可以单独完成的64位整数运算操作。这样一来Core就有了一套64bit的复杂整数单元(这一点和P6核心的CIU相同),以及两个简单整数单元用来处理基本的操作和运算任务。但是非常特别是的是,3个64bit的整数执行单元中的一个简单整数单元和分支执行单元将会共享端口。该端口处的简单整数单元将和分支单元共同完成此处的宏指令结合的任务。 如果说Core架构就是P6架构,那无疑是不公平的。能够独立完成64bit整数运算对Intel x86处理器来说还是头一回,这也让Core得以走在了竞争对手的前列。此外,64bit的整数单元使用彼此独立的数据端口,因此Core能够在一个周期内同时完成3组64bit的整数运算。极强的整数运算单元使得Core在包括游戏、服务器项目、移动等方面都能够发挥广泛而强大的作用。 Core构架的设计图 在以往的NetBurst架构中,浮点单元的性能很一般,这也是为什么AMD处理器总是在3D游戏中有更好表现的原因之一。不过Core构架进行了不小的改进。Core构架拥有2个浮点执行单元同时处理向量和标量的浮点运算,其中一个浮点单元执行负责加减等简单的处理,而另一个浮点单元则执行负责乘除等运算。尽管不能说Core构架令浮点性能有很大幅度的提升,但是其改进效果还是显而易见的。在多项测试中,Conroe台式机处理器已经能够打败AMD高端的FX62。 Core构架的整体效率以及高于AMD K8。如果不是Intel的市场调控能力超强,如今CPU市场的格局可能会是另一番景象。 NorthWood核心为NetBurst架构略微挽回颜面 3.流水线与CPU效率的关系 当然 参考资料:hi.baidu.com/...8.html

声明:本文内容来自用户上传并发布或网络新闻客户端自媒体,本站点仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容,请联系删除。

相关文章

推荐文章

最新文章

- 健康丨中国精神疾病神经调控联盟上海启动 多方聚力促进神经调控领域发

- 健康丨哀悼!深切缅怀我国著名神经病学家郭玉璞教授

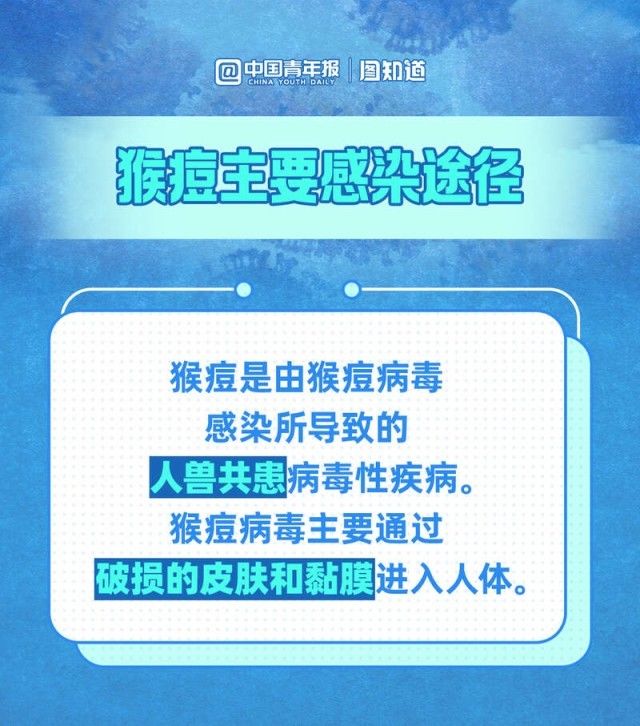

- 健康丨图知道|关注猴痘热点问题,做好科学防护

- 健康丨“晒背养生”掀起热潮,三伏天晒背有用吗?

- 健康丨浙江湖州实施中医药人才三年培养行动计划

- 健康丨别乱喝!这几类人群不宜喝绿豆汤

- 健康丨多地医院推行“一次挂号管三天”,规则有待进一步细化

- 健康丨为啥女性绝经后,不愿意过“夫妻生活”了?这个原因男女都要了解

- 健康丨紫云、镇宁、关岭三县开展协同检查严防严管严控药械安全风险

- 健康丨“养生大师”林海峰离世,享年51岁,反思:这6种养生方法太伤身

- 健康丨头皮发麻!南宁一女子体内惊现大量“瓜子”活虫,只因家人爱吃鱼

- 健康丨治疗干眼症,中医有妙招

- 健康丨9件癌细胞最“怕”的事,一定要多做!快收藏

- 健康丨沪滇协作支持 让多指畸形孩子勇敢伸出双手

- 健康丨(成都大运纪事)保障运动员健康 四川提供特色中医诊疗服务

- 健康丨好男人,不肾虚?若日常出现这6个小毛病,担心肾已经“虚透”!

- 健康丨夏季了解这个小知识,关键时刻能救命!

- 健康丨瘦人得糖尿病,或与这4个因素有关,不想糖尿病找上门,尽量避免

- 健康丨江北:提升基层医疗机构诊疗水平 将优质医疗服务送到群众家门口

- 健康丨南宁国际会展中心将举办“南宁国际成人展”?回应来了